JANUARY 2007 REV. 1.2.2

#### GENERAL DESCRIPTION

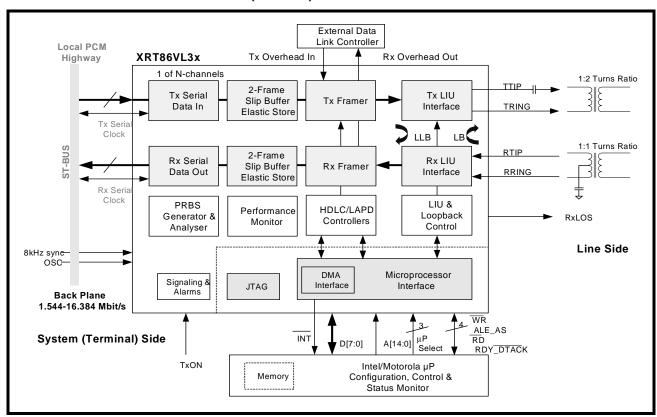

The XRT86VL3x is a 1.544 Mbit/s or 2.048 Mbit/s DS1/E1/J1 framer and LIU integrated solution featuring R<sup>3</sup> technology (Relayless, Reconfigurable, Redundancy) that comes in a 2-channel, 4-channel, or 8-channel package. The physical interface is optimized with internal impedance, and with the patented pad structure, the XRT86VL3x provides protection from power failures and hot swapping.

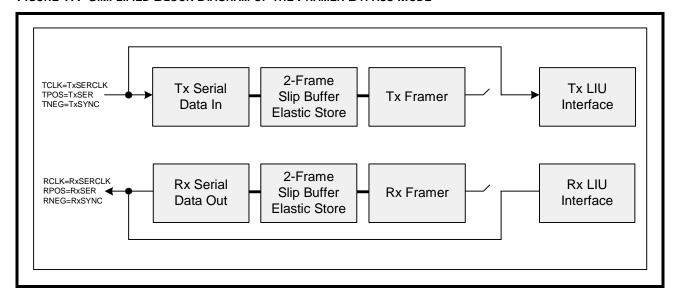

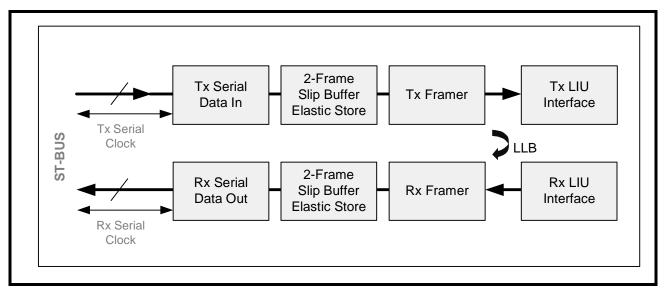

The XRT86VL3x contains an integrated DS1/E1/J1 framer and LIU which provide DS1/E1/J1 framing and error accumulation in accordance with ANSI/ITU\_T specifications. Each framer has its own framing synchronizer and transmit-receive slip buffers. The slip buffers can be independently enabled or disabled as required and can be configured to frame to the common DS1/E1/J1 signal formats.

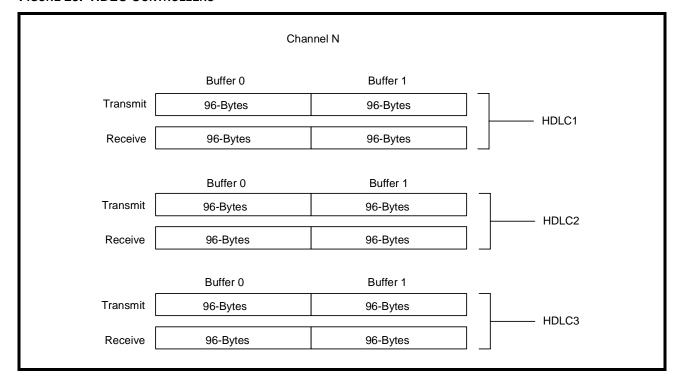

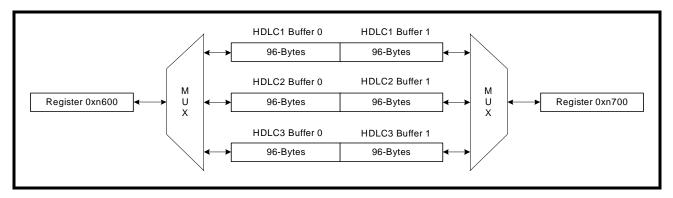

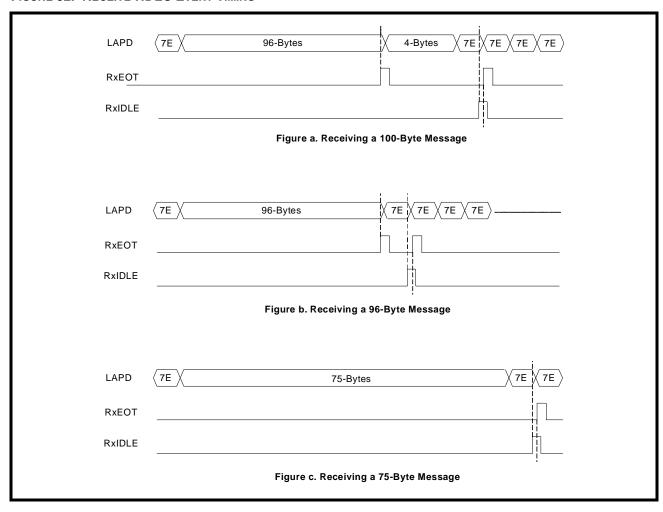

Each Framer block contains its own Transmit and Receive T1/E1/J1 Framing function. There are 3 Transmit HDLC controllers per channel which encapsulate contents of the Transmit HDLC buffers into LAPD Message frames. There are 3 Receive HDLC controllers per channel which extract the

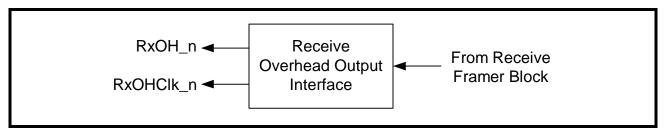

payload content of Receive LAPD Message frames from the incoming T1/E1/J1 data stream and write the contents into the Receive HDLC buffers. Each framer also contains a Transmit and Overhead Data Input port, which permits Data Link Terminal Equipment direct access to the outbound T1/E1/J1 frames. Likewise, a Receive Overhead output data port permits Data Link Terminal Equipment direct access to the Data Link bits of the inbound T1/E1/J1 frames.

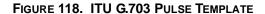

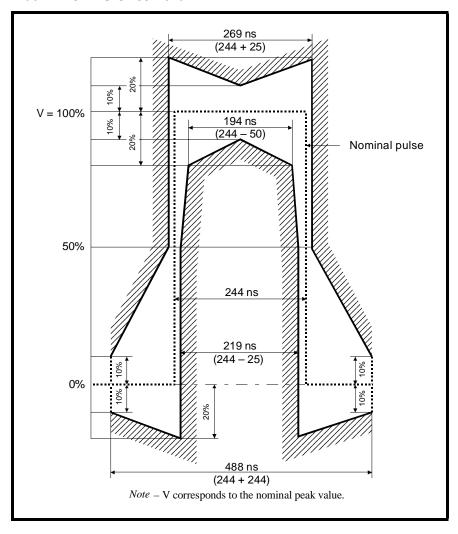

The XRT86VL3x fully meets all of the latest T1/E1/J1 specifications: ANSI T1/E1.107-1988, ANSI T1/E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/E1.408-1990, AT&T TR 62411 (12-90) TR54016, and ITU G-703, G.704, G706 and G.733, AT&T Pub. 43801, and ETS 300 011, 300 233, JT G.703, JT G.704, JT G706, I.431. Extensive test and diagnostic functions include Loop-backs, Boundary scan, Pseudo Random bit sequence (PRBS) test pattern generation, Performance Monitor, Bit Error Rate (BER) meter, forced error insertion, and LAPD unchannelized data payload processing according to ITU-T standard Q.921.

#### **Applications and Features (next page)**

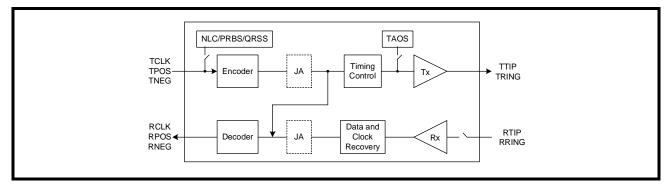

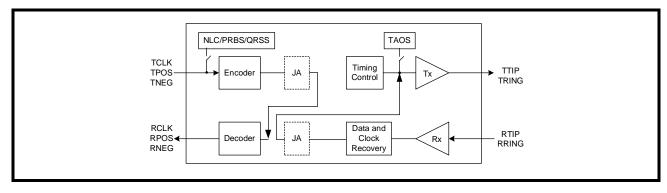

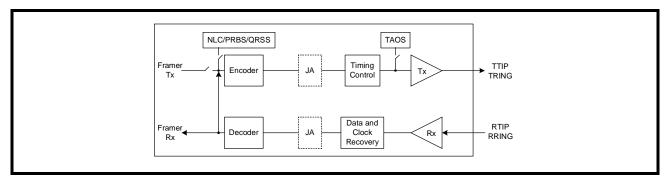

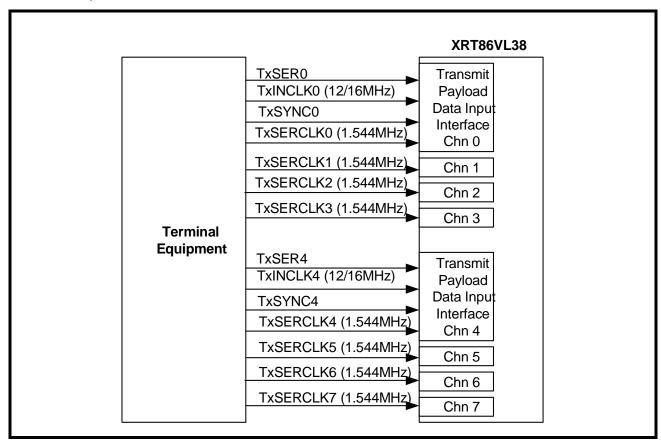

FIGURE 1. XRT86VL3x N-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

#### XRT86VL3X

#### T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION

#### **APPLICATIONS**

- High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

- SONET/SDH terminal or Add/Drop multiplexers (ADMs)

- T1/E1/J1 add/drop multiplexers (MUX)

- Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

- Digital Access Cross-connect System (DACs)

- Digital Cross-connect Systems (DCS)

- Frame Relay Switches and Access Devices (FRADS)

- ISDN Primary Rate Interfaces (PRA)

- PBXs and PCM channel bank

- T3 channelized access concentrators and M13 MUX

- Wireless base stations

- ATM equipment with integrated DS1 interfaces

- Multichannel DS1 Test Equipment

- T1/E1/J1 Performance Monitoring

- Voice over packet gateways

- Routers

#### **FEATURES**

- Independent, full duplex DS1 Tx and Rx Framer/

- Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz asynchronous back plane connections with jitter and wander attenuation

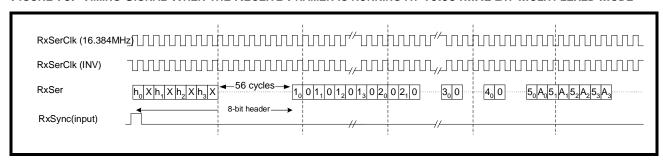

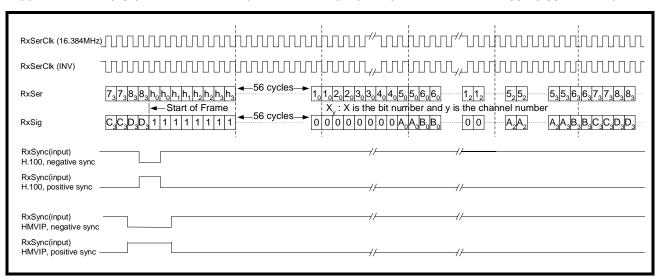

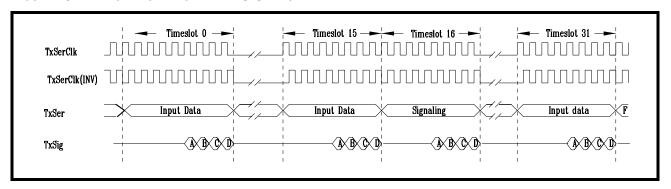

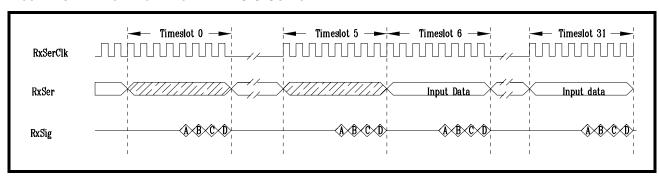

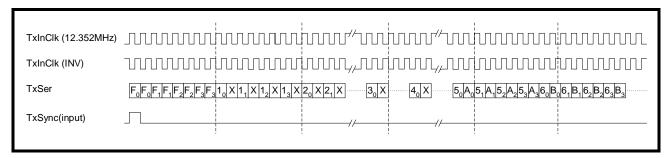

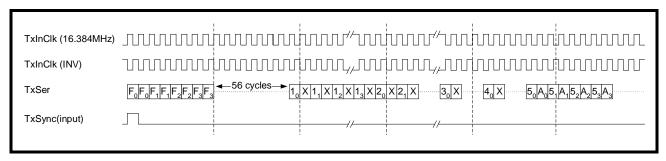

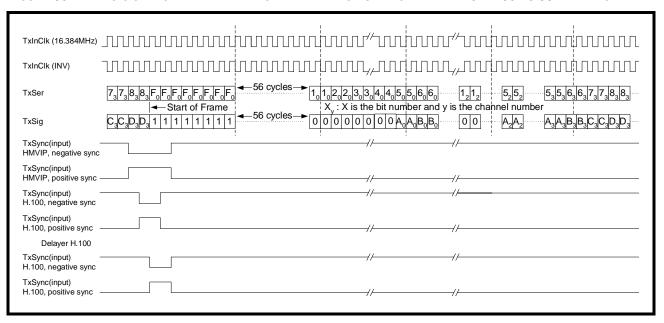

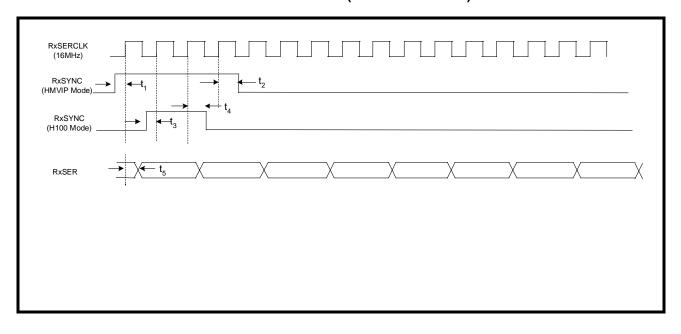

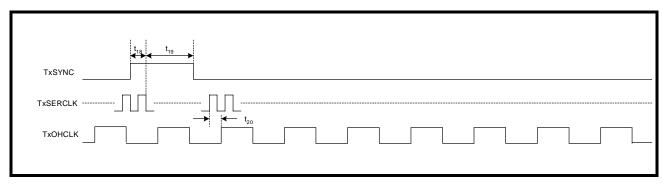

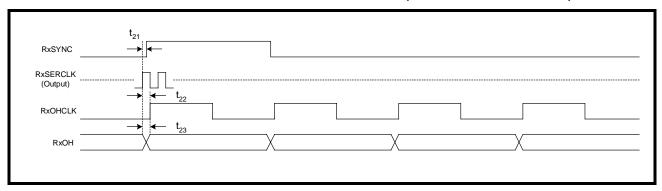

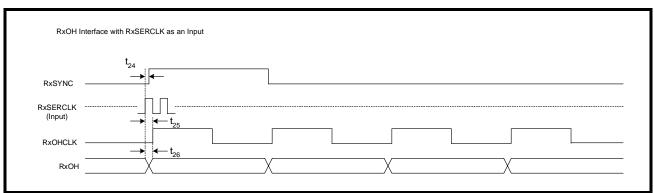

- Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 4channel multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

- Programmable output clocks for Fractional T1/E1/ J1

- Supports Channel Associated Signaling (CAS)

- Supports Common Channel Signalling (CCS)

- Supports ISDN Primary Rate Interface (ISDN PRI) signaling

- Extracts and inserts robbed bit signaling (RBS)

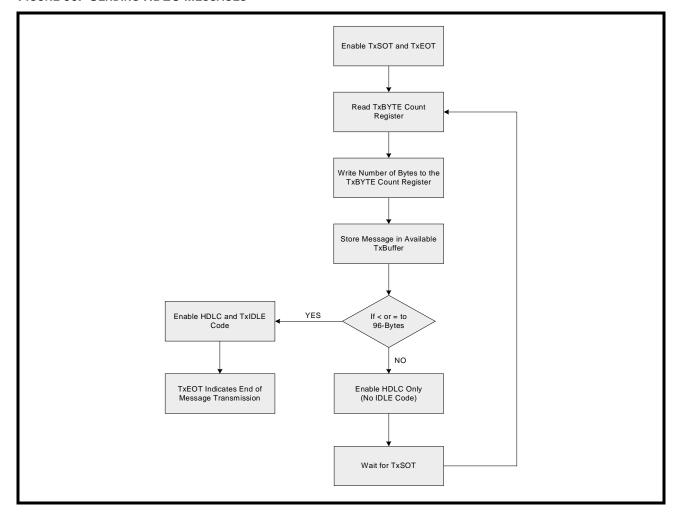

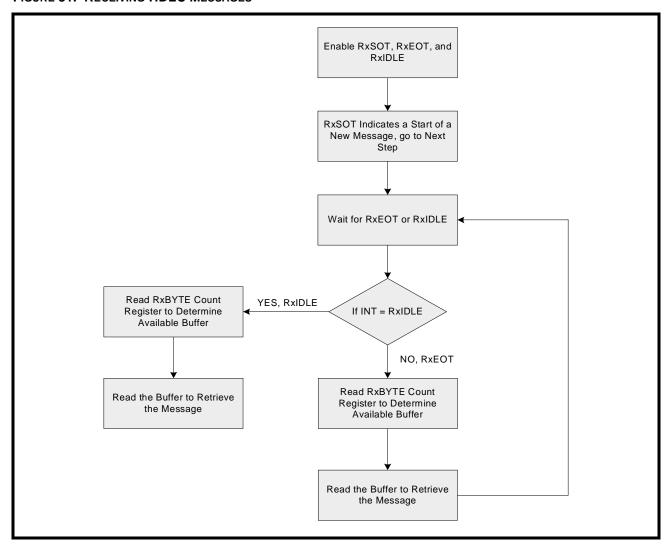

- 3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte buffers (buffer 0 / buffer 1)

- HDLC Controllers Support SS7

- Timeslot assignable HDLC

- V5.1 or V5.2 Interface

- Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface every 1 second or for a single transmission

- Alarm Indication Signal with Customer Installation signature (AIS-CI)

- Remote Alarm Indication with Customer Installation (RAI-CI)

- Gapped Clock interface mode for Transmit and Receive.

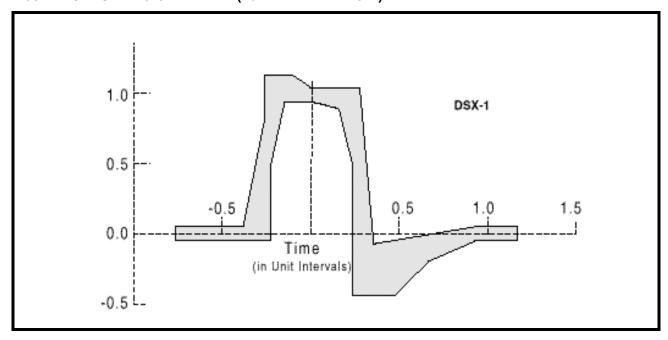

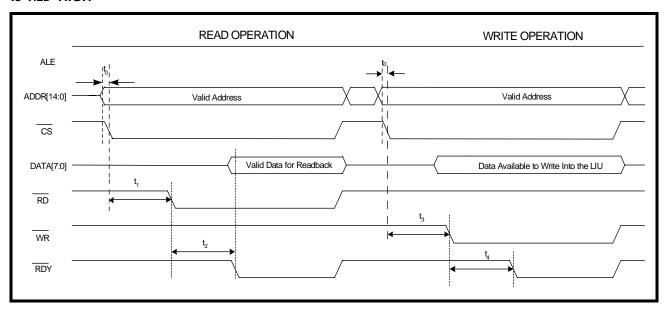

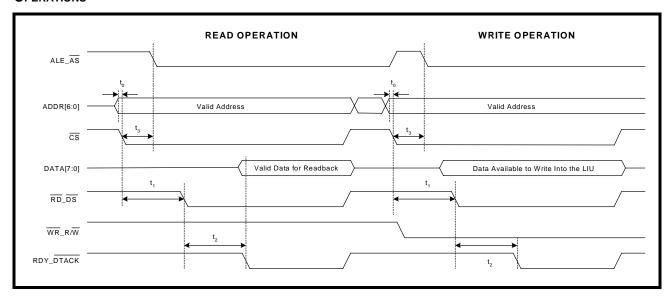

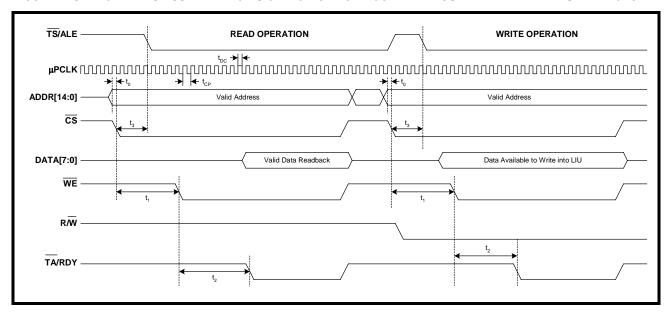

- Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

- Parallel search algorithm for fast frame synchronization

- Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

- Direct access to D and E channels for fast transmission of data link information

- PRBS, QRSS, and Network Loop Code generation and detection

- Programmable Interrupt output pin

- Supports programmed I/O and DMA modes of Read-Write access

- Each framer block encodes and decodes the T1/ E1/J1 Frame serial data

- Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

- Detects OOF, LOF, LOS errors and COFA conditions

- Loopbacks: Local (LLB) and Line remote (LB)

- Facilitates Inverse Multiplexing for ATM

- Performance monitor with one second polling

- Boundary scan (IEEE 1149.1) JTAG test port

- Accepts external 8kHz Sync reference

- 1.8V Inner Core Voltage

- 3.3V I/O operation with 5V tolerant inputs

#### REV. 1.2.2

## **ORDERING INFORMATION**

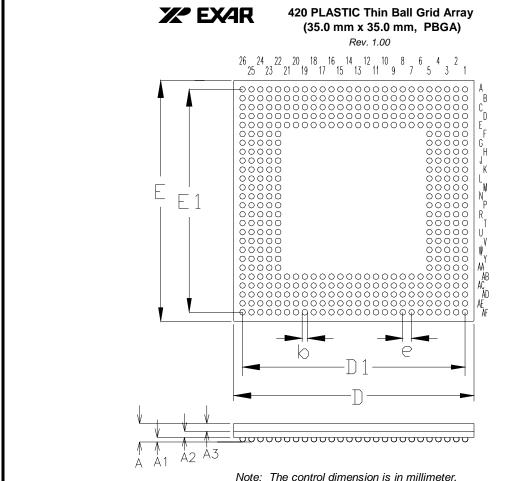

| PART NUMBER    | PACKAGE                         | OPERATING TEMPERATURE RANGE |

|----------------|---------------------------------|-----------------------------|

| XRT86VL38IB    | 420 Tape Ball Grid Array        | -40°C to +85°C              |

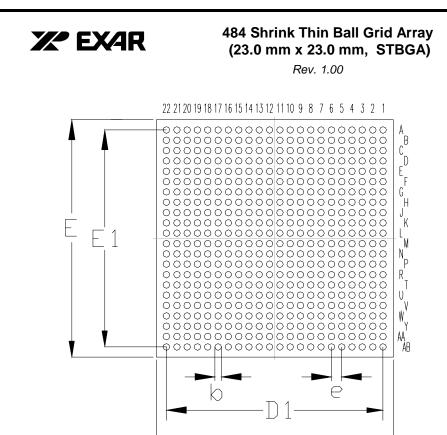

| XRT86VL38IB484 | 484 Shrink Thin Ball Grid Array | -40°C to +85°C              |

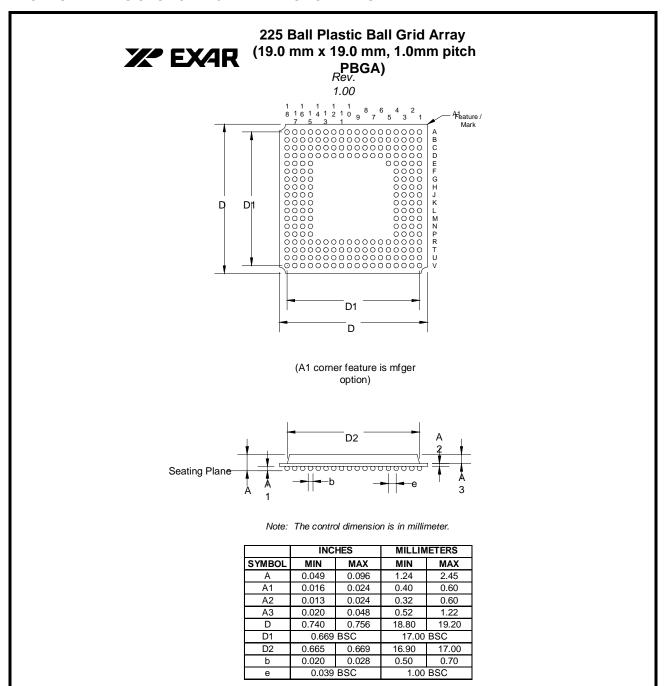

| XRT86VL34IB    | 225 Plastic Ball Grid Array     | -40°C to +85°C              |

| XRT86VL32IB    | 225 Plastic Ball Grid Array     | -40°C to +85°C              |

## LIST OF PARAGRAPHS

| 1.0 GENERAL DESCRIPTION AND INTERFACE                                    | 4  |

|--------------------------------------------------------------------------|----|

| 1.1 PHYSICAL INTERFACE                                                   | 4  |

| 1.2 R3 TECHNOLOGY (RELAYLESS / RECONFIGURABLE / REDUNDANCY)              | 5  |

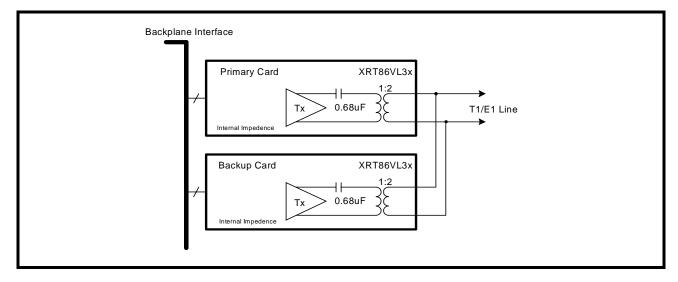

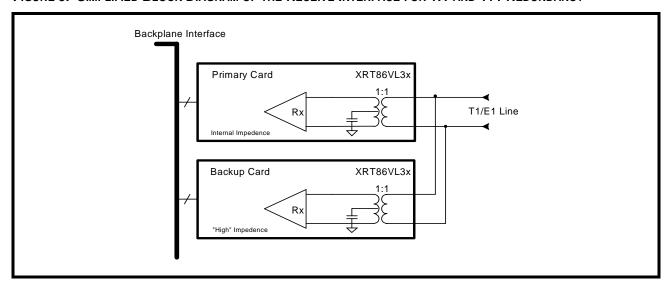

| 1.2.1 LINE CARD REDUNDANCY                                               |    |

| 1.2.2 TYPICAL REDUNDANCY SCHEMES                                         | 5  |

| 1.2.3 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS                              | 5  |

| 1.2.4 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                     |    |

| 1.2.5 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY                      |    |

| 1.3 POWER FAILURE PROTECTION                                             |    |

| 1.4 OVERVOLTAGE AND OVERCURRENT PROTECTION                               |    |

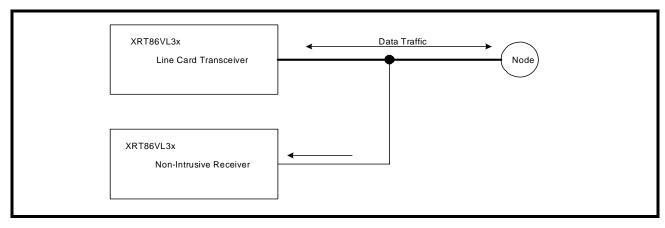

| 1.5 NON-INTRUSIVE MONITORING                                             | 7  |

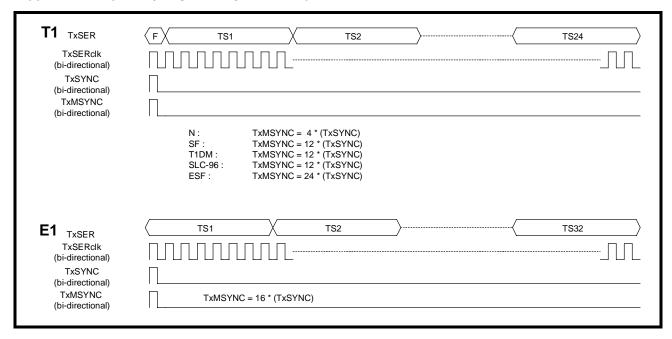

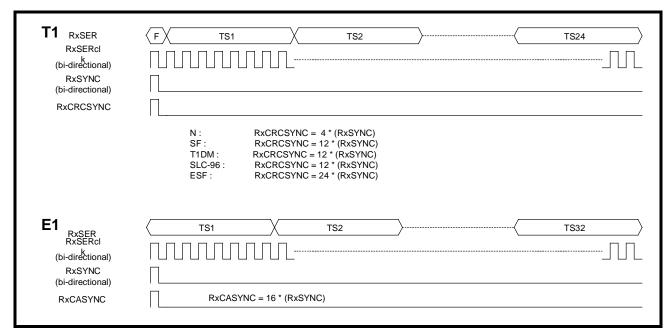

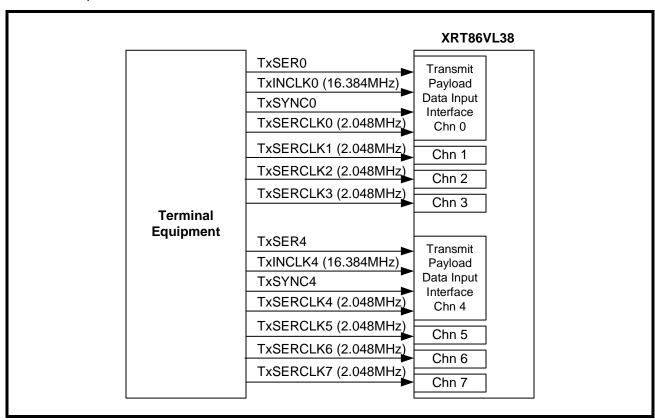

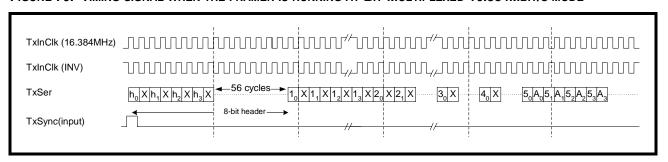

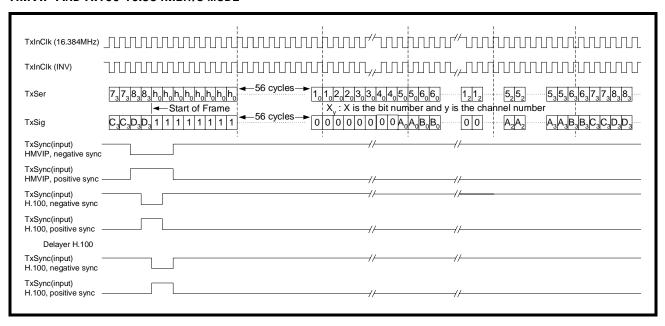

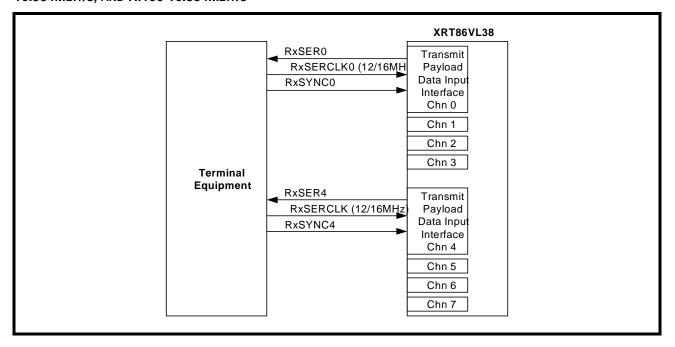

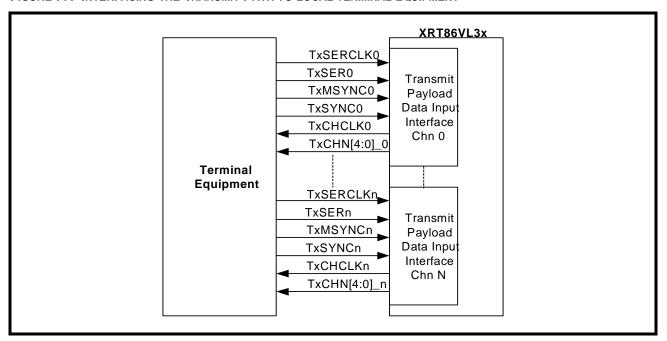

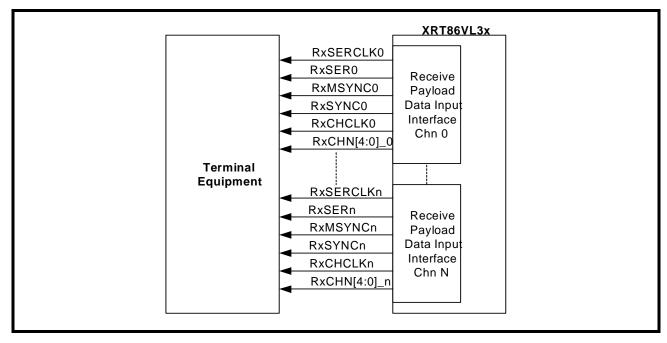

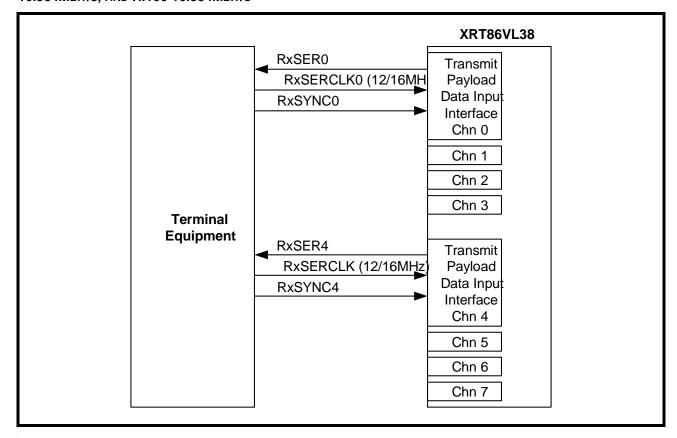

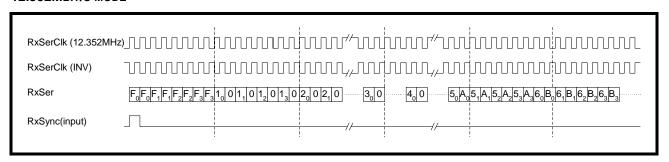

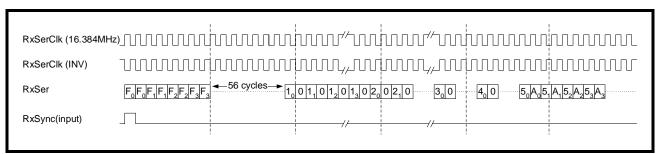

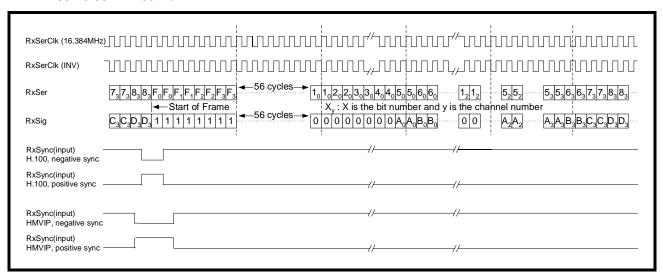

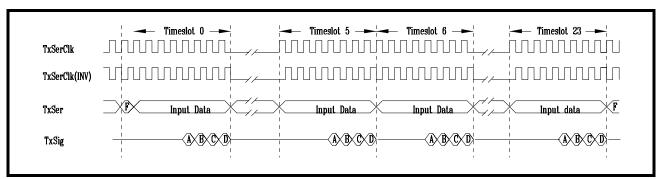

| 1.6 T1/E1 SERIAL PCM INTERFACE                                           | 8  |

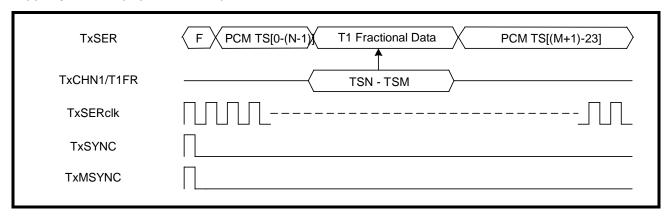

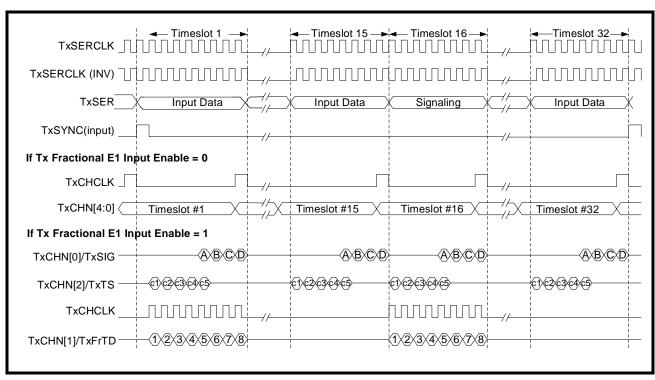

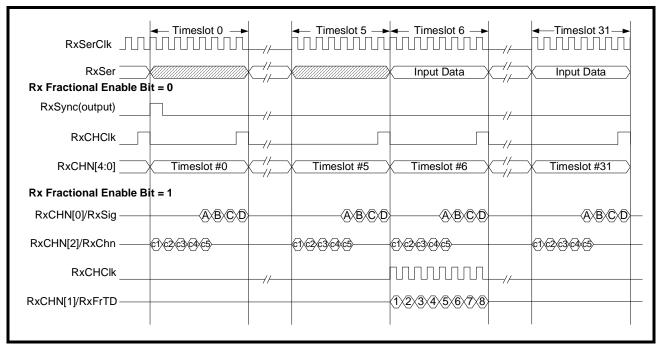

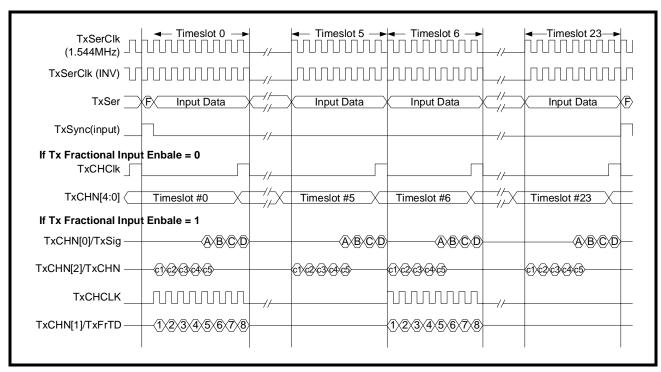

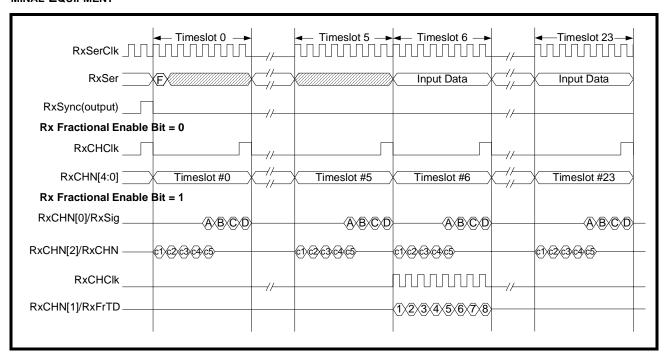

| 1.7 T1/E1 FRACTIONAL INTERFACE                                           | 9  |

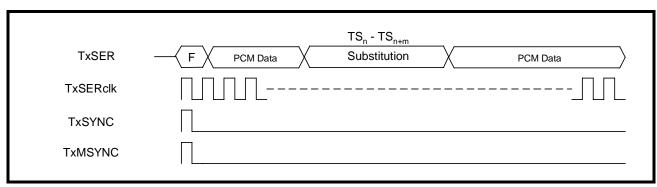

| 1.8 T1/E1 TIME SLOT SUBSTITUTION AND CONTROL                             | 10 |

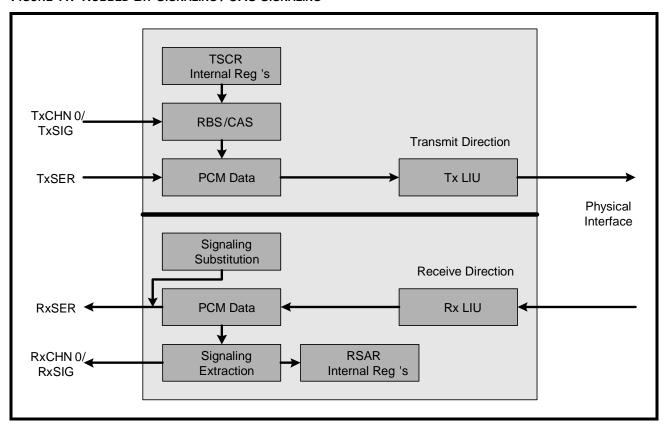

| 1.9 ROBBED BIT SIGNALING/CAS SIGNALING                                   |    |

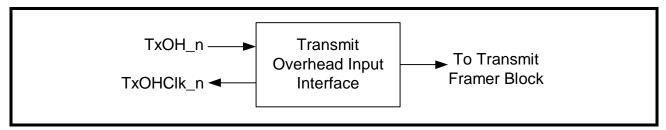

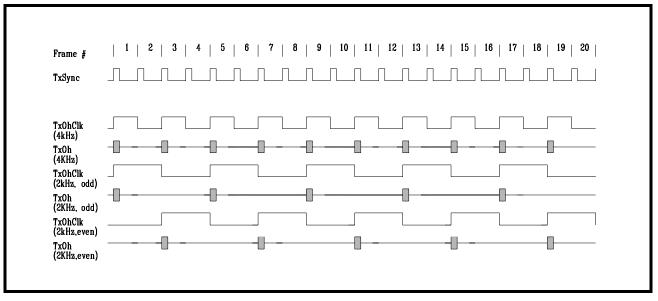

| 1.10 OVERHEAD INTERFACE                                                  |    |

| 1.11 FRAMER BYPASS MODE                                                  |    |

| 1.12 HIGH-SPEED NON-MULTIPLEXED INTERFACE                                |    |

| 1.13 HIGH-SPEED MULTIPLEXED INTERFACE                                    |    |

| 2.0 LOOPBACK MODES OF OPERATION                                          |    |

| 2.1 LIU PHYSICAL INTERFACE LOOPBACK DIAGNOSTICS                          |    |

| 2.1.1 LOCAL ANALOG LOOPBACK                                              |    |

| 2.1.1 LOCAL ANALOG LOOPBACK                                              |    |

| 2.1.3 DIGITAL LOOPBACK                                                   |    |

| 2.1.4 DUAL LOOPBACK                                                      |    |

| 2.1.5 FRAMER REMOTE LINE LOOPBACK                                        |    |

| 2.1.6 FRAMER LOCAL LOOPBACK                                              |    |

| 3.0 HDLC CONTROLLERS AND LAPD MESSAGES                                   |    |

| 3.1 STORING AND RETRIEVING MESSAGE CONTENTS                              |    |

| 3.2 PROGRAMMING SEQUENCE FOR SENDING HDLC MESSAGES                       |    |

| 3.3 PROGRAMMING SEQUENCE FOR RECEIVING LAPD MESSAGES                     |    |

|                                                                          |    |

| 3.4 RECEIVE HDLC EVENT TIMING                                            |    |

| 3.5 SS7 (SIGNALING SYSTEM NUMBER 7) FOR ESF IN DS1 ONLY                  |    |

| 3.6 DS1/E1 DATALINK TRANSMISSION USING THE HDLC CONTROLLERS              |    |

| 3.7 TRANSMIT BOS (BIT ORIENTED SIGNALING) PROCESSOR                      |    |

| 3.7.1 DESCRIPTION OF BOS                                                 |    |

| 3.7.2 PRIORITY CODEWORD MESSAGE                                          |    |

| 3.7.3 COMMAND AND RESPONSE INFORMATION                                   |    |

| 3.8 TRANSMIT MOS (MESSAGE ORIENTED SIGNALING) PROCESSOR                  |    |

| 3.8.1 DISCUSSION OF MOS                                                  |    |

| 3.8.2 PERIODIC PERFORMANCE REPORT                                        |    |

| 3.8.4 PATH AND TEST SIGNAL IDENTIFICATION MESSAGE                        |    |

| 3.8.5 FRAME STRUCTURE                                                    |    |

| 3.8.6 FLAG SEQUENCE                                                      |    |

| 3.8.7 ADDRESS FIELD                                                      |    |

| 3.8.8 ADDRESS FIELD EXTENSION BIT (EA)                                   |    |

| 3.8.9 COMMAND OR RESPONSE BIT (C/R)                                      |    |

| 3.8.10 SERVICE ACCESS POINT IDENTIFIER (SAPI)                            |    |

| 3.8.11 TERMINAL ENDPOINT IDENTIFIER (TEI)                                |    |

| 3.8.12 CONTROL FIELD                                                     | 29 |

| 3.8.13 FRAME CHECK SEQUENCE (FCS) FIELD                                  |    |

| 3.8.14 TRANSPARENCY (ZERO STUFFING)                                      |    |

| 3.9 TRANSMIT SLC®96 DATA LINK CONTROLLER                                 | 30 |

| 3.10 D/E TIME SLOT TRANSMIT HDLC CONTROLLER BLOCK V5.1 OR V5.2 INTERFACE | 31 |

| 3.11 AUTOMATIC PERFORMANCE REPORT (APR)                                  |    |

| 3.11.1 BIT VALUE INTERPRETATION                                          |    |

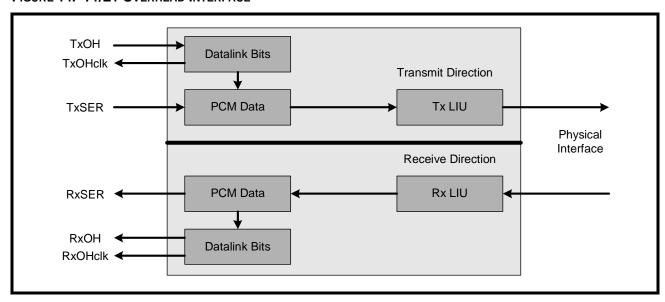

| 4.0 OVERHEAD INTERFACE BLOCK                                             |    |

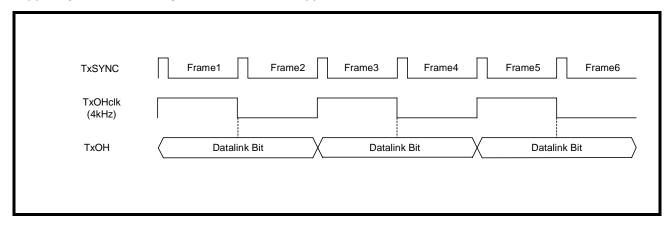

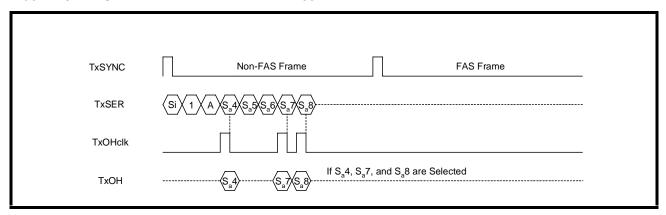

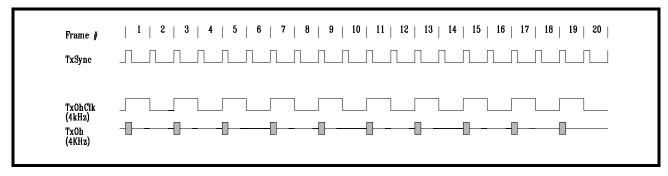

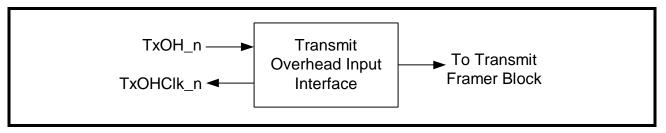

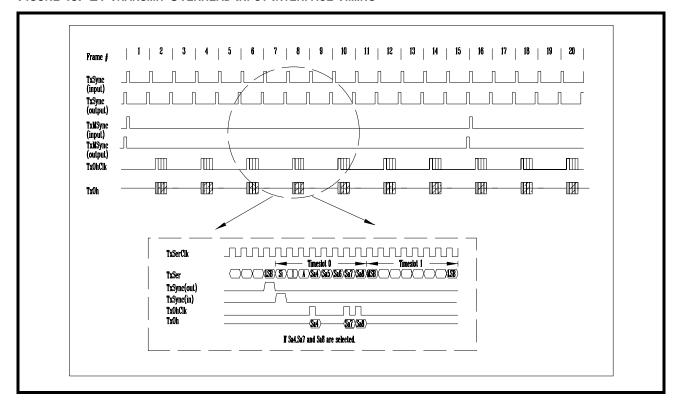

| 4.1 DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK                          |    |

| 4.1.1 DESCRIPTION OF THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK     |    |

|     | 4.1.2 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE FACILITY I | DATA  |

|-----|----------------------------------------------------------------------------------------------|-------|

|     | LINK (FDL) BITS IN ESF FRAMING FORMAT MODE                                                   | . 33  |

|     | FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE                                         |       |

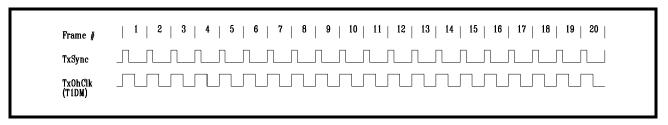

|     | 4.1.4 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE REMOTE S   | SIG-  |

|     | NALING (R) BITS IN T1DM FRAMING FORMAT MODE                                                  | . 36  |

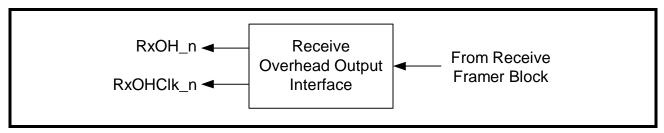

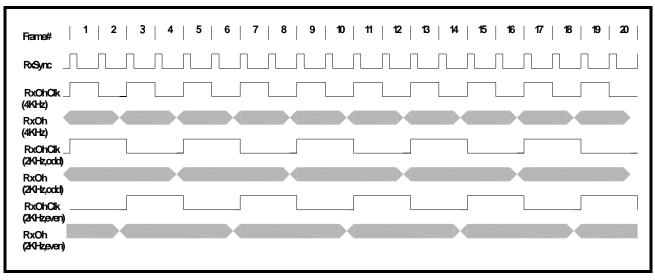

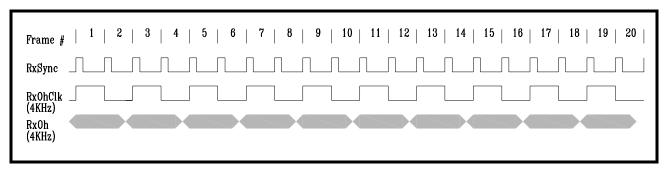

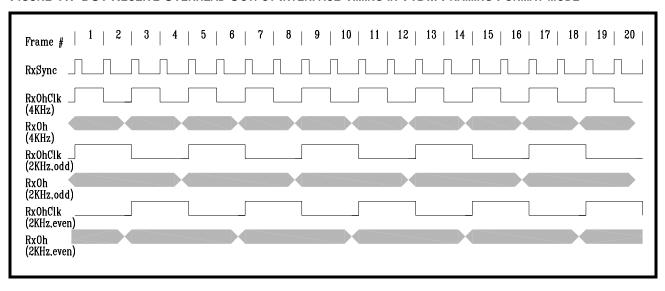

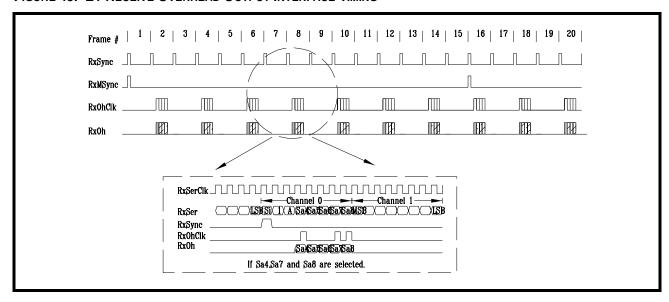

|     | 4.2 DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK                                              | . 37  |

|     | 4.2.1 DESCRIPTION OF THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK                         | . 37  |

|     | 4.2.2 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE FAC   | ILITY |

|     | DATA LINK (FDL) BITS IN ESF FRAMING FORMAT MODE                                              | . 37  |

|     | 4.2.3 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE SIGNA |       |

|     | FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE                                         | . 39  |

|     | 4.2.4 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE REM   |       |

|     | SIGNALING (R) BITS IN T1DM FRAMING FORMAT MODE                                               | . 40  |

|     | 4.3 E1 OVERHEAD INTERFACE BLOCK                                                              |       |

|     | 4.4 E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK                                               |       |

|     | 4.4.1 DESCRIPTION OF THE E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK                          |       |

|     | QUENCE IN E1 FRAMING FORMAT MODE                                                             |       |

|     | 4.5 E1 RECEIVE OVERHEAD INTERFACE                                                            |       |

|     | 4.5.1 DESCRIPTION OF THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK                          |       |

|     | 4.5.2 CONFIGURE THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS SOURCE OF THE NATIONAL    |       |

|     | SEQUENCE IN E1 FRAMING FORMAT MODE                                                           |       |

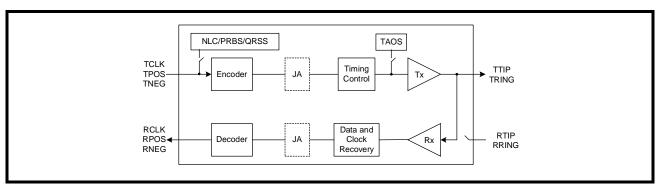

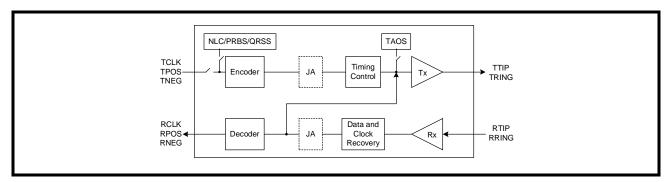

| 5.0 | LIU TRANSMIT PATH                                                                            | _     |

| 0.0 | 5.1 TRANSMIT DIAGNOSTIC FEATURES                                                             |       |

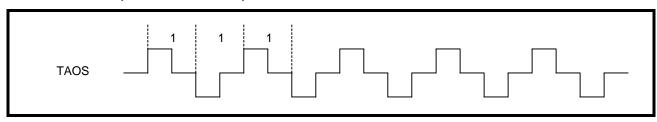

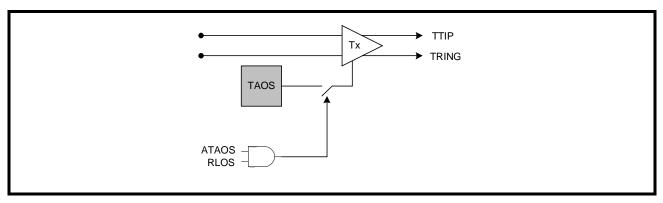

|     | 5.1.1 TAOS (TRANSMIT ALL ONES)                                                               |       |

|     | 5.1.2 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                                    | . 47  |

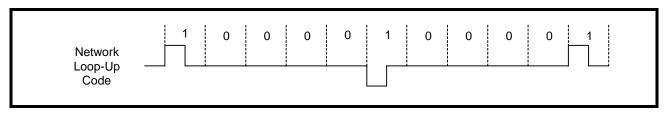

|     | 5.1.3 NETWORK LOOP UP CODE                                                                   |       |

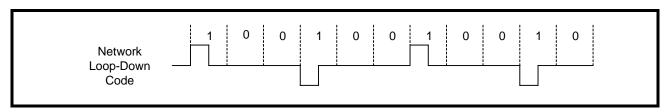

|     | 5.1.4 NETWORK LOOP DOWN CODE                                                                 | . 48  |

|     | 5.1.5 QRSS GENERATION                                                                        |       |

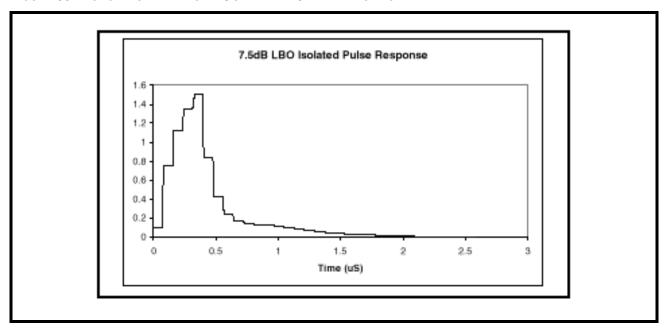

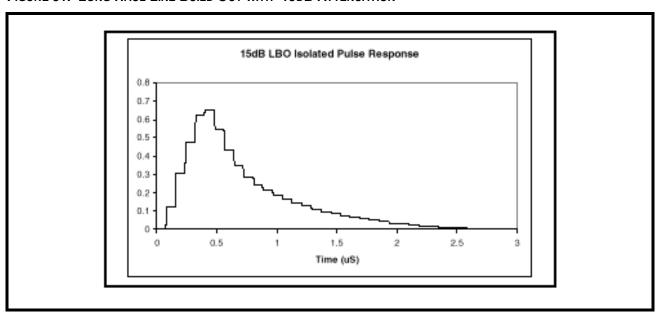

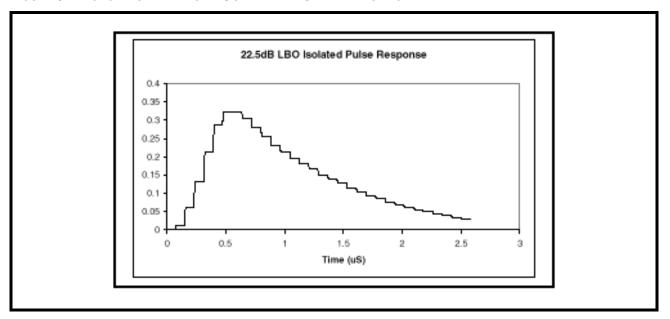

|     | 5.2 T1 LONG HAUL LINE BUILD OUT (LBO)                                                        |       |

|     | 5.3 T1 SHORT HAUL LINE BUILD OUT (LBO)                                                       | . 51  |

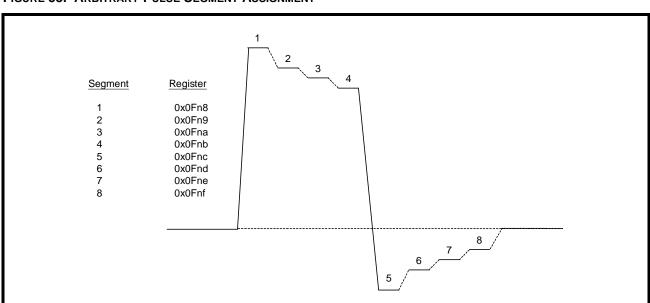

|     | 5.3.1 ARBITRARY PULSE GENERATOR                                                              |       |

|     | 5.3.2 DMO (DIGITAL MONITOR OUTPUT)                                                           | . 52  |

|     | 5.3.3 TRANSMIT JITTER ATTENUATOR                                                             |       |

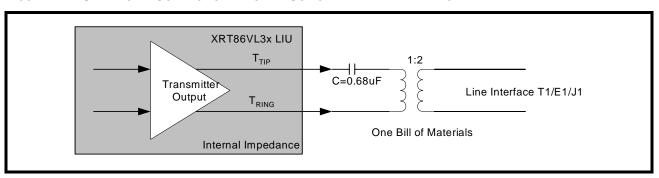

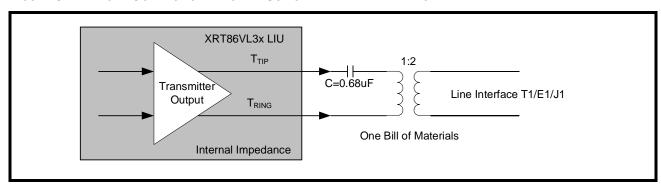

|     | 5.4 LINE TERMINATION (TTIP/TRING)                                                            |       |

| 6.0 | LIU RECEIVE PATH                                                                             |       |

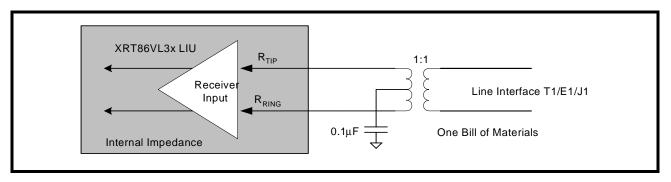

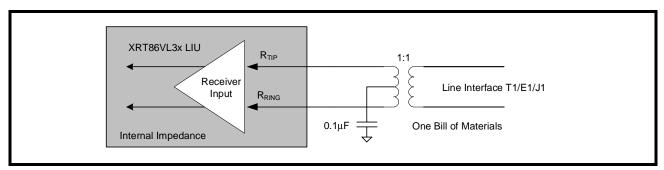

|     | 6.1 LINE TERMINATION (RTIP/RRING)                                                            |       |

|     | 6.1.1 INTERNAL TERMINATION                                                                   |       |

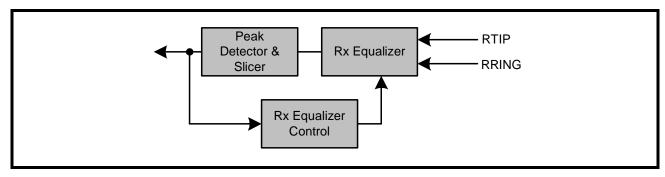

|     | 6.1.2 EQUALIZER CONTROL                                                                      |       |

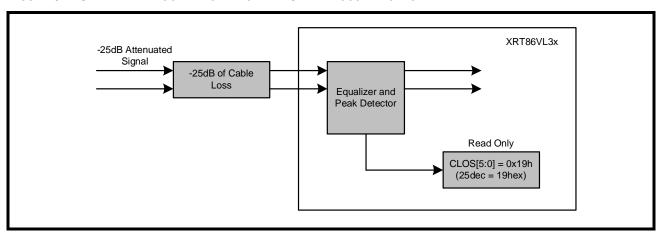

|     | 6.1.3 CABLE LOSS INDICATOR                                                                   |       |

|     | 6.2 RECEIVE SENSITIVITY                                                                      |       |

|     | 6.2.1 AIS (ALARM INDICATION SIGNAL)                                                          |       |

|     | 6.2.3 FLSD (FIFO LIMIT STATUS DETECTION)                                                     |       |

|     | 6.2.4 RECEIVE JITTER ATTENUATOR                                                              |       |

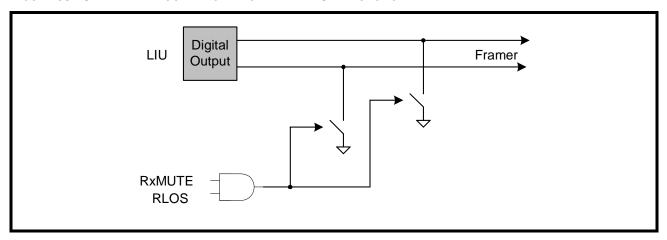

|     | 6.2.5 RXMUTE (RECEIVER LOS WITH DATA MUTING)                                                 |       |

| 7.0 | THE E1 TRANSMIT/RECEIVE FRAMER                                                               |       |

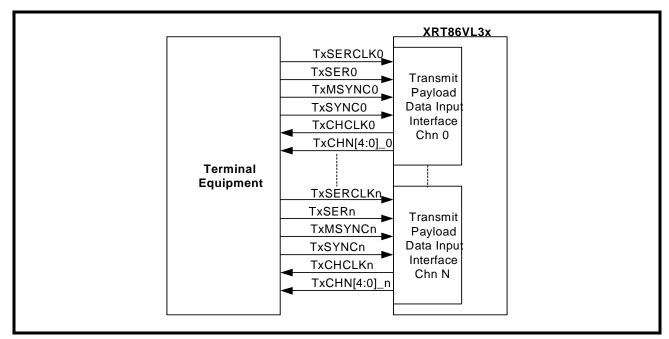

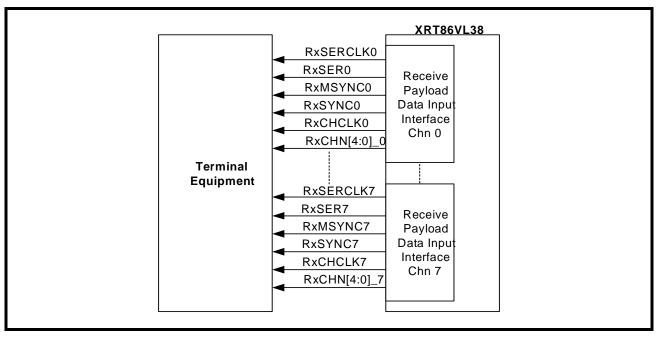

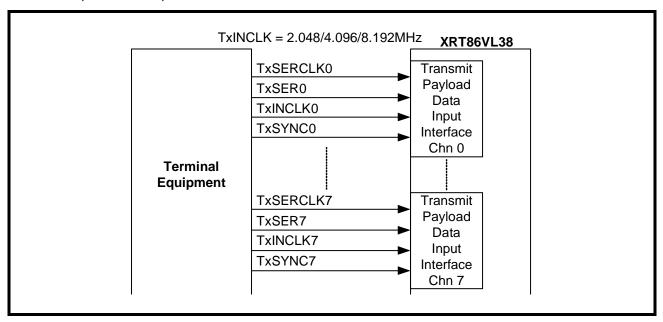

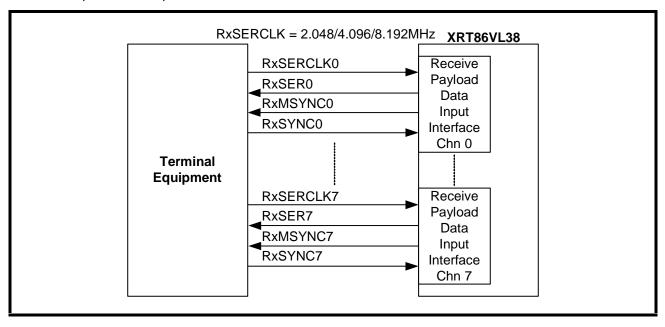

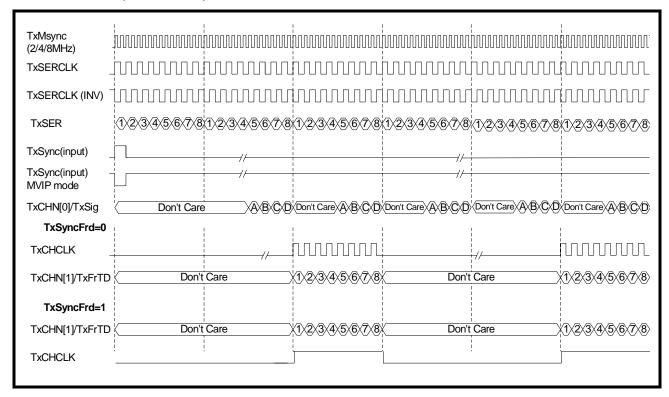

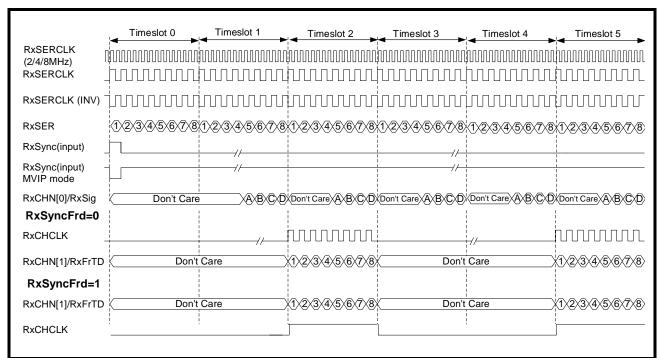

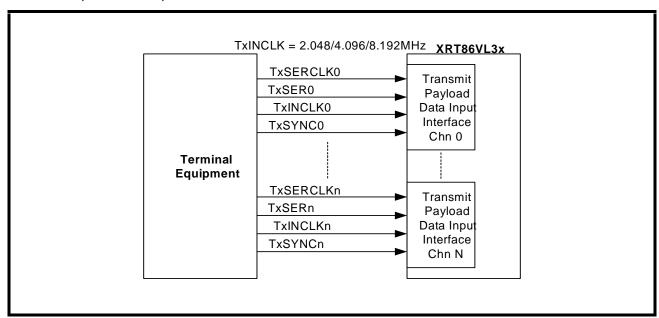

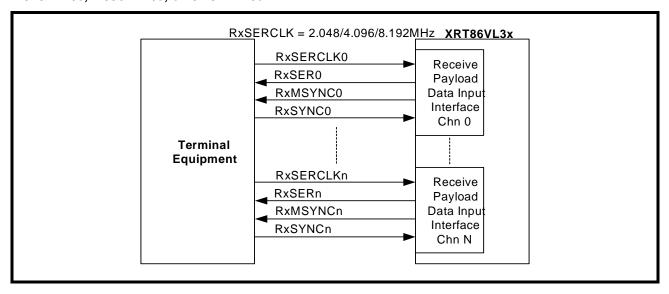

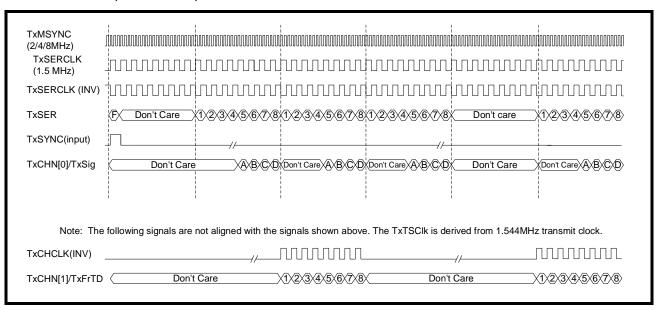

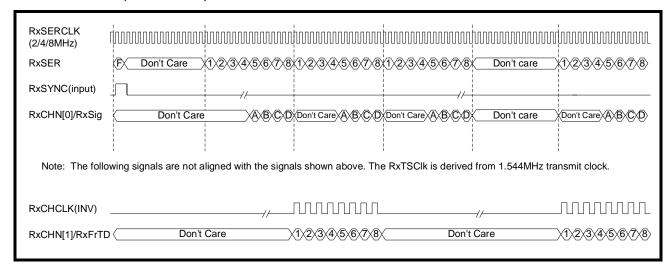

| 0   | 7.1 DESCRIPTION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK                   |       |

|     | 7.1.1 BRIEF DISCUSSION OF THE TRANSMIT/RECEIVE PAYLOAD DATA IN OT INTERFACE BLOCK OPERATING  |       |

|     | XRT84V24 COMPATIBLE 2.048MBIT/S MODE                                                         |       |

|     | 7.2 TRANSMIT/RECEIVE HIGH-SPEED BACK-PLANE INTERFACE                                         |       |

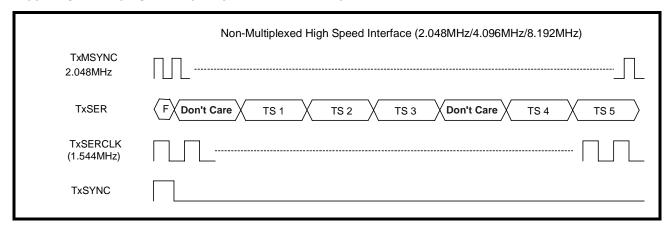

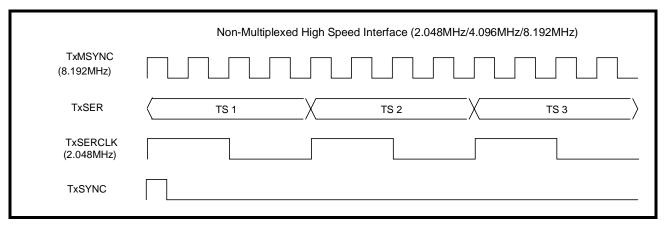

|     | 7.2.1 NON-MULTIPLEXED HIGH-SPEED MODE                                                        |       |

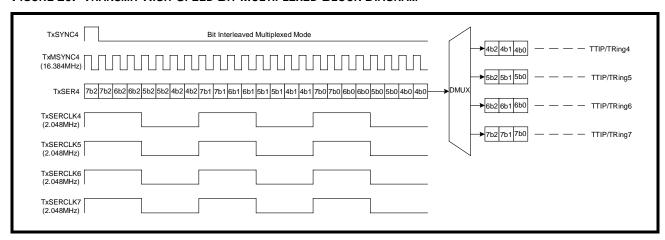

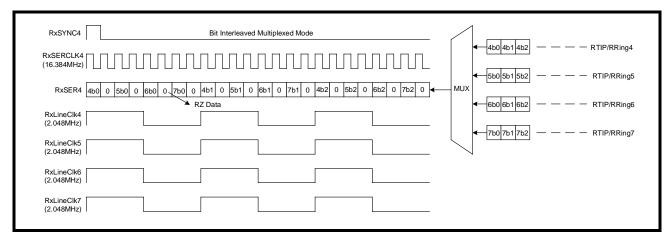

|     | 7.2.2 MULTIPLEXED HIGH-SPEED MODE                                                            | . 63  |

|     | 7.3 BRIEF DISCUSSION OF COMMON CHANNEL SIGNALING IN E1 FRAMING FORMAT                        | . 69  |

|     | 7.4 BRIEF DISCUSSION OF CHANNEL ASSOCIATED SIGNALING IN E1 FRAMING FORMAT                    | . 69  |

|     | 7.5 INSERT/EXTRACT SIGNALING BITS FROM TSCR REGISTER                                         |       |

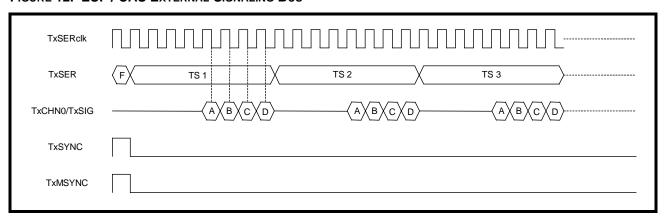

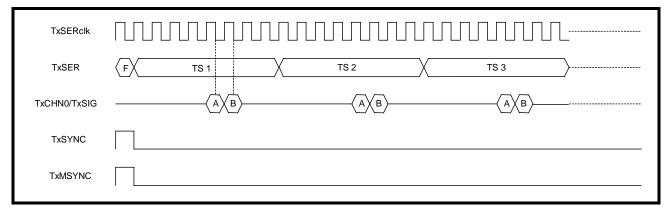

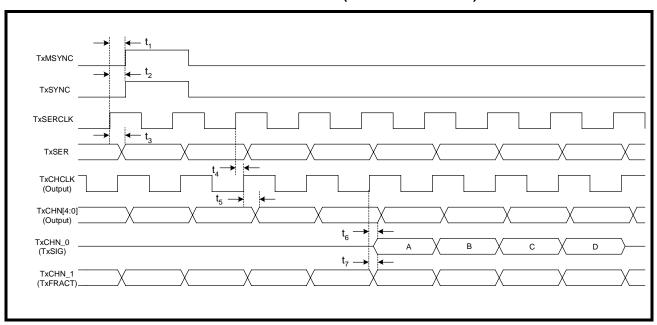

|     | 7.6 INSERT/EXTRACT SIGNALING BITS FROM TXCHN[0]_N/TXSIG PIN                                  |       |

|     | 7.7 ENABLE CHANNEL ASSOCIATED SIGNALING AND SIGNALING DATA SOURCE CONTROL                    | . 70  |

| 8.0 | THE DS1 TRANSMIT/RECEIVE FRAMER                                                              |       |

| ٠.٠ | 8.1 DESCRIPTION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK                   |       |

|     | 8.1.1 BRIEF DISCUSSION OF THE TRANSMIT/RECEIVE PAYLOAD DATA IN OT INTERFACE BLOCK OPERATING  |       |

|     | 1.544MBIT/S MODE                                                                             |       |

|     | 8.2 TRANSMIT/RECEIVE HIGH-SPEED BACK-PLANE INTERFACE                                         |       |

|     |                                                                                              |       |

## XRT86VL3X

## **EXAR**

# Experience Our Connectivity. REV. 1.2.2

## T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION

| 8.2.2 NON-MULTIPLEXED HIGH-SPEED MODE       74         8.2.3 MULTIPLEXED HIGH-SPEED MODE       76         8.3 BRIEF DISCUSSION OF ROBBED-BIT SIGNALING IN DS1 FRAMING FORMAT       85         8.3.1 CONFIGURE THE FRAMER TO TRANSMIT ROBBED-BIT SIGNALING       86         8.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER       86         8.3.3 INSERT SIGNALING BITS FROM TSCR REGISTER       86         9.0 ALARMS AND ERROR CONDITIONS       89         9.1 AIS ALARM       89         9.2 RED ALARM       91         9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GREARTE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       104         9.6.4 TRANSMIT YELLOW ALARM       104         9.6.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE <th></th> <th></th> <th></th>                                                                                                                                                        |   |                                                            |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------|-----|

| 8.23 MULTIPLEXED HIGH-SPEED MODE  8.3 BRIEF DISCUSSION OF ROBBED-BIT SIGNALING IN DS1 FRAMING FORMAT  8.5 8.3.1 CONFIGURE THE FRAMER TO TRANSMIT ROBBED-BIT SIGNALING  8.6 8.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER  8.7 9.0 ALARMS AND ERROR CONDITIONS  9.1 AIS ALARM  9.2 RED ALARM  9.2 RED ALARM  9.3 YELLOW ALARM  9.4 BIPOLAR VIOLATION  9.5 1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS  9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS  9.5.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS  9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM  9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM  9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS  9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM  9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM  9.6.7 TRANSMIT CAS MULTI-FRAME TO GENERATE RED ALARM  9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM  9.6.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM  9.6.6 THARSMIT YELLOW ALARM NO BEROR CONDITIONS  9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS  9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM  10.9 9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM  10.9 9.6.4 TRANSMIT YELLOW ALARM IN SF MODE  110  9.6.5 TRANSMIT YELLOW ALARM IN SF MODE  110  9.6.6 TRANSMIT YELLOW ALARM IN SF MODE  110  9.6.7 TRANSMIT YELLOW ALARM IN TIDM MODE  110  10.1 THE E1 FRAMING STRUCTURE  1112  10.1.1 FAS FRAME  112  10.1.1 FAS FRAME  113  10.2 THE E1 MULTI-FRAME STRUCTURE  114 |   | 8.2.1 T1 TRANSMIT/RECEIVE INTERFACE - MVIP 2.048 MHZ       |     |

| 8.3 BRIEF DISCUSSION OF ROBBED-BIT SIGNALING IN DS1 FRAMING FORMAT 85 8.3.1 CONFIGURE THE FRAMER TO TRANSMIT ROBBED-BIT SIGNALING 86 8.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER 86 8.3.3 INSERT SIGNALING BITS FROM TSCIR REGISTER 87 9.0 ALARMS AND ERROR CONDITIONS 89 9.1 AIS ALARM 89 9.2 RED ALARM 99 9.2 RED ALARM 99 9.3 YELLOW ALARM 99 9.4 BIPOLAR VIOLATION 94 9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS 96 9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS 102 9.5.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS 103 9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM 103 9.5.4 TRANSMIT YELLOW ALARM 104 9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM 104 9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS 105 9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS 104 9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM 104 9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM 104 9.6.4 TRANSMIT YELLOW ALARM 105 9.6.5 TRANSMIT YELLOW ALARM IN SF MODE 110 9.6.5 TRANSMIT YELLOW ALARM IN SF MODE 110 9.6.6 TRANSMIT YELLOW ALARM IN SF MODE 110 9.6.7 TRANSMIT YELLOW ALARM IN SF MODE 110 9.6.7 TRANSMIT YELLOW ALARM IN SF MODE 110 9.6.7 TRANSMIT YELLOW ALARM IN TIPM MODE 110 10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS 112 10.1 THE E1 FRAMING STRUCTURE 112 10.1.1 FAS FRAME 112 10.1.2 NON-FAS FRAME 112 10.1.2 NON-FAS FRAME 113 10.2 THE E1 MULTI-FRAME STRUCTURE 114                                                                  |   |                                                            |     |

| 8.3.1 CONFIGURE THE FRAMER TO TRANSMIT ROBBED-BIT SIGNALING       86         8.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER       86         8.3.3 INSERT SIGNALING BITS FROM TXSIG_N PIN       87         9.0 ALARMS AND ERROR CONDITIONS       89         9.1 AIS ALARM       89         9.2 RED ALARM       91         9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       103         9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN TOMODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMA                                                                                                                                                                                  |   | ·-·                                                        |     |

| 8.3.2 INSERT SIGNALING BITS FROM TSCR REGISTER       86         8.3.3 INSERT SIGNALING BITS FROM TXSIG_N PIN       87         9.0 ALARMS AND ERROR CONDITIONS       89         9.1 AIS ALARM       89         9.2 RED ALARM       91         9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       103         9.5.4 TRANSMIT YELLOW ALARM       104         9.6 TI BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN TIDM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAME STRUCTURE                                                                                                                                                                                             | 8 |                                                            |     |

| 8.3.3 INSERT SIGNALING BITS FROM TXSIG_N PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                            |     |

| 9.0 ALARMS AND ERROR CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                            |     |

| 9.1 AIS ALARM       89         9.2 RED ALARM       91         9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       103         9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN TIDM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 PAS FRAME       112         10.2.1 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                               |   |                                                            |     |

| 9.2 RED ALARM       91         9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.7 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN NODE       110         9.6.7 TRANSMIT YELLOW ALARM IN TIDM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.2 THE E1 MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                  |   |                                                            |     |

| 9.3 YELLOW ALARM       92         9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       103         9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.7 THOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN TIOM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.2 NON-FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       11                                                                                                                                                                                           | ( | 9.1 AIS ALARM                                              | 89  |

| 9.4 BIPOLAR VIOLATION       94         9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       104         9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.5.7 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN TIDM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                          | , | 9.2 RED ALARM                                              | 91  |

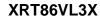

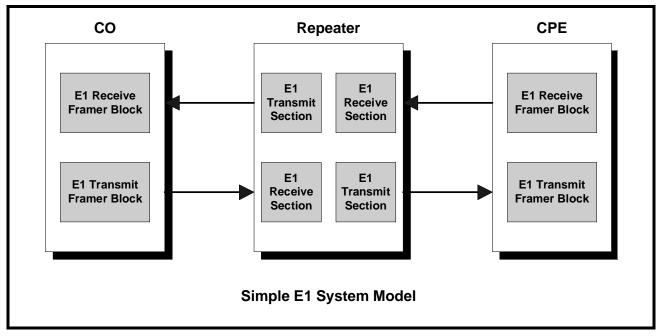

| 9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       96         9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       102         9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       103         9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT YELLOW ALARM       104         9.6.7 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6.7 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                 | ( | 9.3 YELLOW ALARM                                           | 92  |

| 9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ( | 9.4 BIPOLAR VIOLATION                                      | 94  |

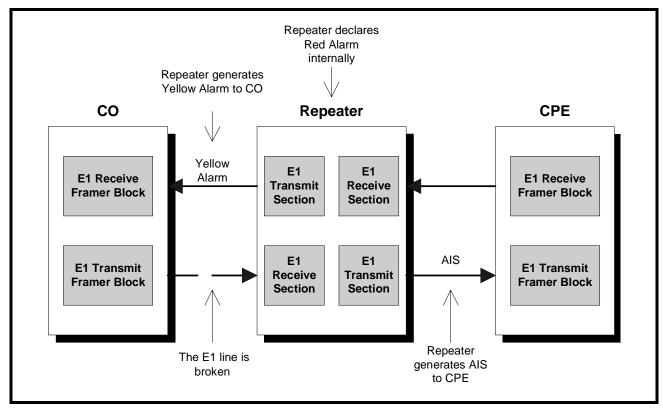

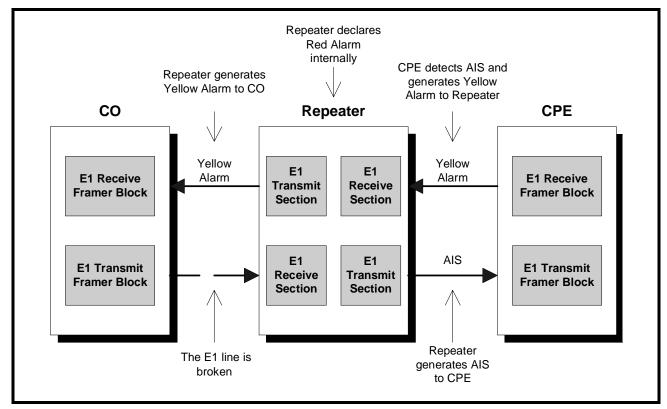

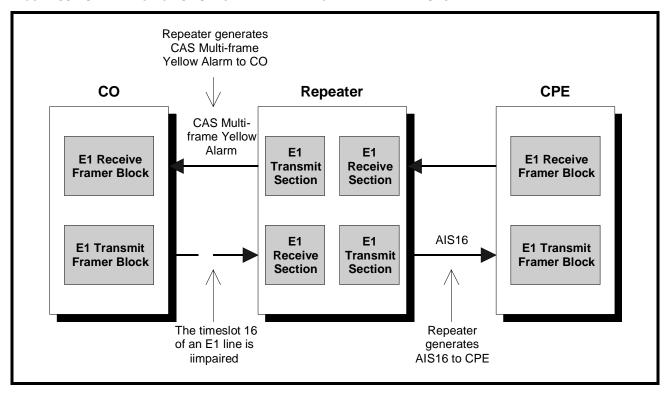

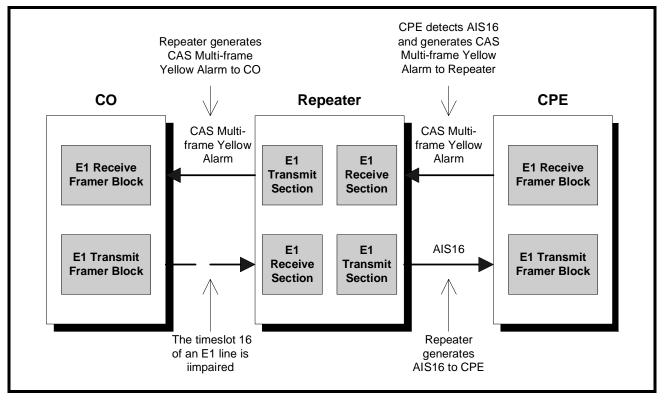

| 9.5.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ( | 9.5 E1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS     | 96  |

| 9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       103         9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN N MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                            |     |

| 9.5.4 TRANSMIT YELLOW ALARM       104         9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 9.5.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM    | 103 |

| 9.5.5 TRANSMIT CAS MULTI-FRAME YELLOW ALARM       104         9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN N MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 9.5.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM | 103 |

| 9.6 T1 BRIEF DISCUSSION OF ALARMS AND ERROR CONDITIONS       105         9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                                                            |     |

| 9.6.1 HOW TO CONFIGURE THE FRAMER TO TRANSMIT AIS       108         9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN RESF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                                            |     |

| 9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM       109         9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM       109         9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN RESF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ( |                                                            |     |

| 9.6.3 HOW TO CONFIGURE THE FRAMER TO TRANSMIT YELLOW ALARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                            |     |

| 9.6.4 TRANSMIT YELLOW ALARM IN SF MODE       110         9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 9.6.2 HOW TO CONFIGURE THE FRAMER TO GENERATE RED ALARM    | 109 |

| 9.6.5 TRANSMIT YELLOW ALARM IN ESF MODE       110         9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                            |     |

| 9.6.6 TRANSMIT YELLOW ALARM IN N MODE       110         9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | ***************************************                    |     |

| 9.6.7 TRANSMIT YELLOW ALARM IN T1DM MODE       110         10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                                            |     |

| 10.0 APPENDIX A: DS-1/E1 FRAMING FORMATS       112         10.1 THE E1 FRAMING STRUCTURE       112         10.1.1 FAS FRAME       112         10.1.2 NON-FAS FRAME       113         10.2 THE E1 MULTI-FRAME STRUCTURE       114         10.2.1 THE CRC MULTI-FRAME STRUCTURE       114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                            |     |

| 10.1 THE E1 FRAMING STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                            |     |

| 10.1.1 FAS FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                                                            |     |

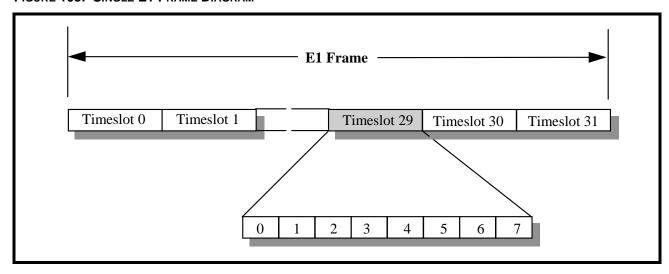

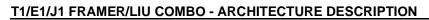

| 10.1.2 NON-FAS FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • | 10.1 THE E1 FRAMING STRUCTURE                              | 112 |

| 10.2 THE E1 MULTI-FRAME STRUCTURE114  10.2.1 THE CRC MULTI-FRAME STRUCTURE114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 10.1.1 FAS FRAME                                           | 112 |

| 10.2.1 THE CRC MULTI-FRAME STRUCTURE114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | 10.2 THE E1 MULTI-FRAME STRUCTURE                          | 114 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 10.2.2 CAS MULTI-FRAMES AND CHANNEL ASSOCIATED SIGNALING   |     |

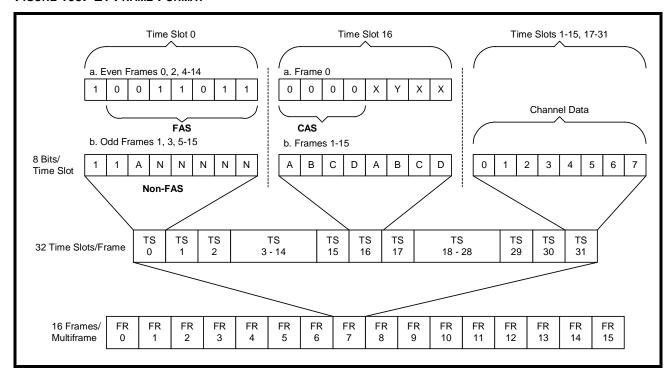

| 10.3 THE DS1 FRAMING STRUCTURE117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 10.3 THE DS1 FRAMING STRUCTURE                             | 117 |

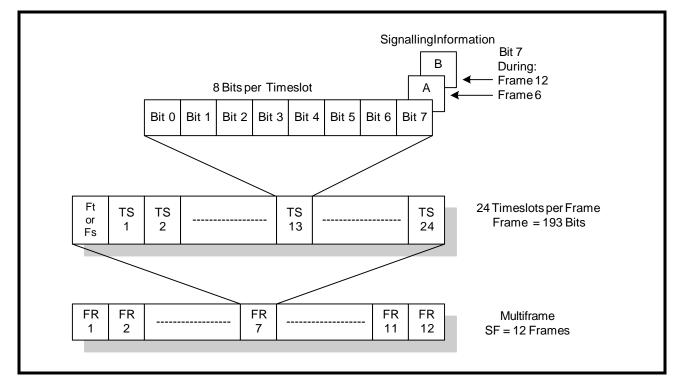

| 10.4 T1 SUPER FRAME FORMAT (SF)118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                                            |     |

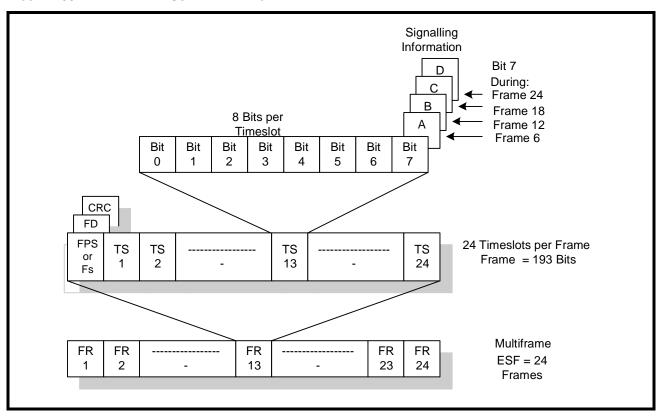

| 10.5 T1 EXTENDED SUPERFRAME FORMAT (ESF)119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 10.5 T1 EXTENDED SUPERFRAME FORMAT (ESF)                   | 119 |

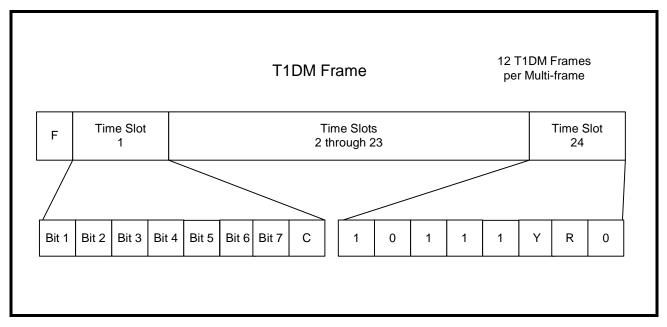

| 10.6 T1 NON-SIGNALING FRAME FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 10.6 T1 NON-SIGNALING FRAME FORMAT                         | 121 |